- 您现在的位置:买卖IC网 > Sheet目录1203 > COREPCIF-RM (Microsemi SoC)IP MODULE COREPCIF

�� �

�

�

�Clock� and� Reset� Networks�

�Clock� and� Reset� Networks�

�The� core� includes� global� buffers� for� both� the� PCI� clock� and� reset� inputs.� The� buffered� versions� of� these� signals� are�

�provided� on� the� CLK_OUT� and� RST_OUTN� ports.� These� should� be� used� for� clocking� and� resetting� any� additional�

�logic� included� in� the� FPGA� running� of� the� PCI� clock.�

�The� core� also� uses� two� additional� global� resources� for� internal� routing� of� the� high-fanout� TRDYN� and� IRDYN� nets,� if�

�required.� Target� cores� will� require� IRDYN� to� be� routed� on� a� global;� if� the� Master� function� is� implemented,� the� TRDYN�

�net� will� be� routed� on� a� global� network.�

�In� SX-A� and� RTSX-S� implementations� with� both� Master� and� Target� functions� enabled,� the� reset� network� is� demoted� to�

�a� normal� buffer� tree,� as� there� are� only� three� global� resources� available� in� these� devices.� They� are� required� for� the� clock�

�and� the� TRDYN� and� IRDYN� nets.�

�Assigning� Pin� Layout� Constraints�

�You� can� assign� pins� manually� with� the� PinEditor� tool� or� import� them� directly� into� Designer� from� the� corresponding� pin�

�constraint� file.� The� pin� file� will� be� a� PIN,� GCF,� or� PDC� file,� depending� on� the� FPGA� family� being� used.�

�Pin� Assignments�

�To� be� able� to� meet� the� critical� PCI� setup,� hold,� and� clock-to-out� requirements,� it� is� critical� that� the� PCI� pin� locations� be�

�assigned� correctly.� Two� aspects� need� to� be� considered:�

�1.�

�2.�

�Pin� assignments� should� minimize� FPGA� place-and-route� issues.� Pin� assignment� is� extremely� important� in� meeting�

�the� PCI� setup,� hold,� and� clock-to-out� requirements.�

�Pin� assignments� should� minimize� PCB� layout� issues.� The� PCI� specification� limits� the� track� lengths� allowed� on� the�

�PCB.� Chapter� 4� of� the� PCI� specification� details� the� requirements.�

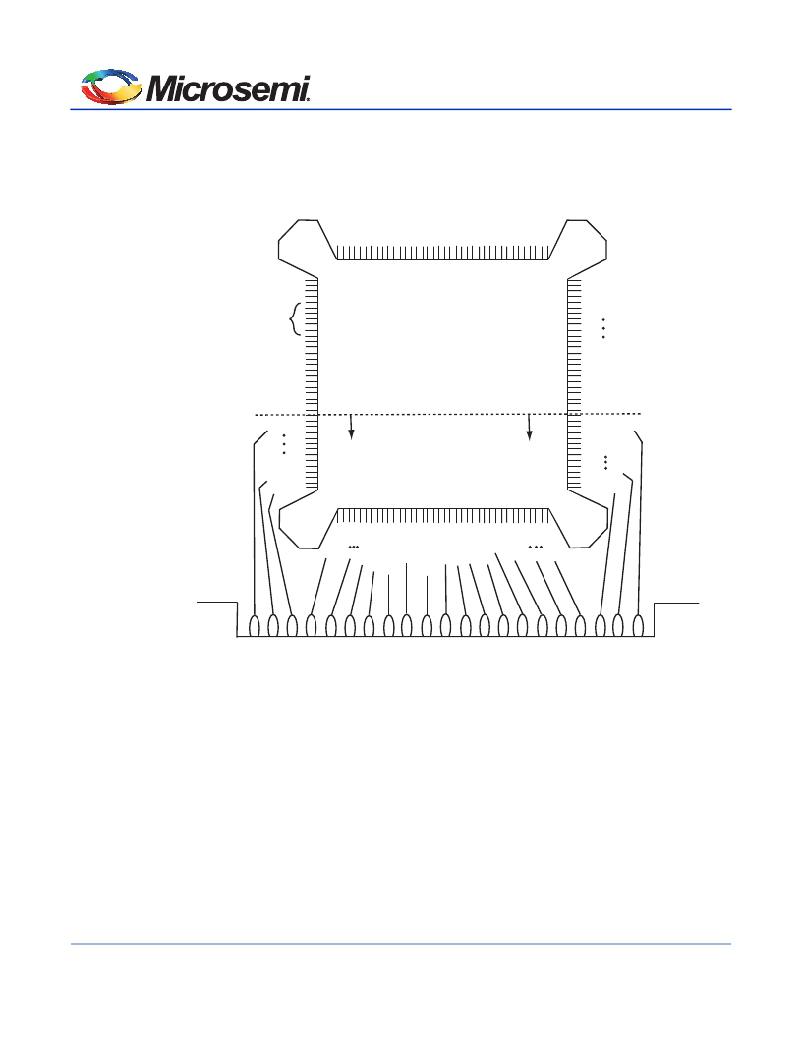

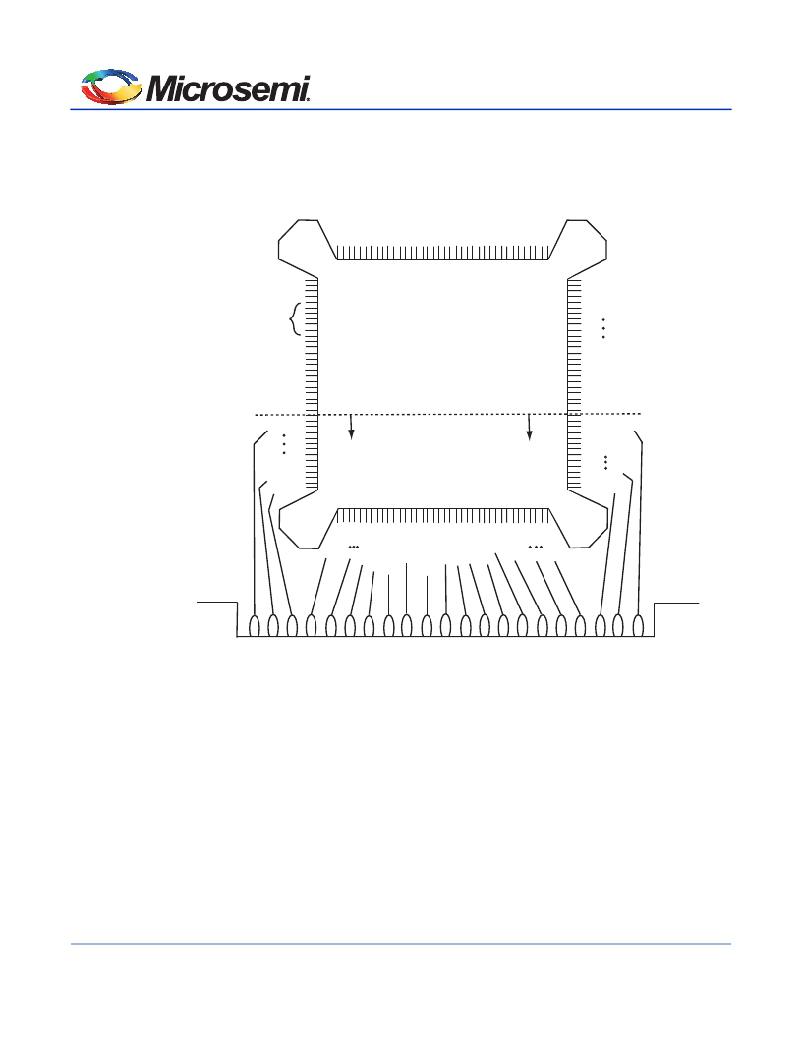

�The� PCI� specification� recommends� that� the� pin� order� around� the� device� align� exactly� with� the� add-in� card� (connector)�

�pinout.� The� additional� signals� needed� in� 64-bit� versions� of� the� bus� continue� wrapping� around� the� component� in� a�

�counterclockwise� direction� in� the� same� order� they� appear� on� the� 64-bit� connector� extension.� “PCI� Pinout� ”� on� page� 135�

�provides� details� of� the� recommended� pin� order.�

�Example� pin� files� are� provided� in� the� layout� directory� for� some� of� the� possible� FPGA� family,� device,� and� package�

�combinations.� These� can� be� adapted� to� support� other� device/package� combinations.�

�Each� supported� FPGA� family� has� different� requirements� to� minimize� FPGA� layout� issues;� these� are� detailed� below.�

�SX-A� and� RTSX-S� Families�

�The� pins� should� be� located� around� one� side� of� the� package� in� the� order� specified� by� the� PCI� specification.� The� pins�

�should� be� located� on� the� same� side� of� the� package� where� CLKA� and� CLKB� are� located.�

�1.�

�2.�

�3.�

�Locate� TRDYN� and� IRDYN� close� to� the� CLKA� and� CLKB� pins,� but� do� not� use� these� pins.�

�Assign� the� rest� of� the� PCI� pins� around� the� package� in� the� order� that� will� match� the� add-in� connector.� Do� not� use�

�any� of� the� CLK,� QCLK,� or� HCLK� pins.�

�Connect� the� PCI� CLK� to� the� HCLK� pin.�

�ProASIC� PLUS� Family�

�The� pins� should� be� located� around� one� side� of� the� package� in� the� order� specified� by� the� PCI� specification.� The� pins�

�should� be� located� on� the� west� side� of� the� die� (in� the� pin� editor,� these� pins� will� be� identified� by� a� “W� ”� on� the� pin),�

�depending� on� the� package� type.� This� may� be� the� left� or� right� side� of� the� package.�

�1.�

�Locate� TRDYN� and� IRDYN� close� to� the� GL� inputs.�

�v4.0�

�129�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

COREU1LL-AR

IP MODULE COREU1LL

COREU1PHY-AR

IP MODULE COREU1PHY

CORR-8BIT-XM-UT2

SITE LICENSE IP CORRELATOR XP

CP2-GSA-L

CONN SHIELD LOWER TYPE A 22

CP2-HSA110-1

CONN SHROUD CPCI 2MM TYPE A 22

CP2-HSC055-4

CONN SHROUD CPCI 2MM TYPE C 11

CP2-K3567-SR-F

COMPACT PCI - MISC

CP2105EK

KIT EVAL FOR CP2105

相关代理商/技术参数

COREPCIF-RMFL

功能描述:IP MODULE 制造商:microsemi corporation 系列:- 零件状态:在售 类型:许可证 应用:- 版本:- 许可长度:- 许可 - 用户明细:- 操作系统:- 配套使用产品/相关产品:Microsemi 器件 媒体分发类型:- 标准包装:1

COREPCIF-UR

功能描述:HW/SW/OTHER 制造商:microsemi corporation 系列:* 零件状态:在售 标准包装:1

COREPCI-SN

制造商:ACTEL 制造商全称:Actel Corporation 功能描述:CorePCI v5.41

COREPCI-SR

制造商:ACTEL 制造商全称:Actel Corporation 功能描述:CorePCI v5.41

COREPCI-UR

制造商:ACTEL 制造商全称:Actel Corporation 功能描述:CorePCI v5.41

COREPCI-XX

制造商:ACTEL 制造商全称:Actel Corporation 功能描述:CorePCI v5.41

COREPRO LEDBULB 10.5-60W B

制造商:Philips Lumileds 功能描述:

COREPRO LEDBULB 10.5-60W E

制造商:Philips Lumileds 功能描述: